## Current on/off ratio enhancement through the electrical burning process in ambient with/without oxygen for the generation of high-performance aligned single-walled carbon nanotube field effect transistors

Sunkook Kim, In Su Park, Hyuk-Jun Kwon, Woo-Jin Chang, and Sang Woo Lee

Citation: Applied Physics Letters **97**, 173102 (2010); doi: 10.1063/1.3504689 View online: http://dx.doi.org/10.1063/1.3504689 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/97/17?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Direct current injection and thermocapillary flow for purification of aligned arrays of single-walled carbon nanotubes J. Appl. Phys. **117**, 134303 (2015); 10.1063/1.4916537

Ultra-short suspended single-wall carbon nanotube transistors Appl. Phys. Lett. **99**, 243106 (2011); 10.1063/1.3670055

Current on/off ratio enhancement of field effect transistors with bundled carbon nanotubes J. Appl. Phys. **106**, 104505 (2009); 10.1063/1.3253737

High-density horizontally aligned growth of carbon nanotubes with Co nanoparticles deposited by arcdischarge plasma method Appl. Phys. Lett. **93**, 053112 (2008); 10.1063/1.2969290

Electrowetting devices with transparent single-walled carbon nanotube electrodes Appl. Phys. Lett. **90**, 093124 (2007); 10.1063/1.2561032

## Current on/off ratio enhancement through the electrical burning process in ambient with/without oxygen for the generation of high-performance aligned single-walled carbon nanotube field effect transistors

Sunkook Kim,<sup>1</sup> In Su Park,<sup>2</sup> Hyuk-Jun Kwon,<sup>1</sup> Woo-Jin Chang,<sup>3</sup> and Sang Woo Lee<sup>2,a)</sup> <sup>1</sup>Samsung Advanced Institute of Technology, Mt. 14-1, Nongseo-dong, Giheung-gu, Yongin-Si,

Gyeonggi-do 446-712, Republic of Korea

<sup>2</sup>Department of Biomedical Engineering, Yonsei University, Wonju, Gangwon 220-710, Republic of Korea <sup>3</sup>Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Illinois 61801, USA

(Received 10 May 2010; accepted 24 September 2010; published online 25 October 2010)

We present characteristics of the electrical burning process with/without oxygen-ambient for parallel aligned single-walled carbon nanotube field effect transistors (SWNT-FETs). High selectivity of metallic and semiconducting nanotubes is demonstrated by an electrical burning process through partial etching of the atomic layer deposited Al<sub>2</sub>O<sub>3</sub> layer beneath the gate electrodes. Metallic nanotubes exposed to oxygen show electrical breakdown during the burning process, resulting in the SWNT-FETs having excellent performance. Specifically, 100  $\mu$ m source/drain width p-type aligned SWNT-FETs through electrical burning with local oxidation show high  $I_{on}/I_{off}$  ratios (>10<sup>3</sup>), 10  $\mu$ S at a drain bias of -1 V and  $-100 \ \mu$ A at a reverse gate bias of -8 V. © 2010 American Institute of Physics. [doi:10.1063/1.3504689]

Single-walled carbon nanotube field effect transistors (SWNT-FETs) have been the focal point of the research on devices for electronic circuit applications and integrated sensors, due to their excellent electrical properties (e.g., ballistic transport and high current capability), which originate from their one-dimensional nanostructure.<sup>1–4</sup> For the implementation of large integrated circuits and high performance devices, advanced growth techniques and fabrication methods have been studied intensively with a view toward producing Si complimentary metal-oxide-semiconductors.<sup>3–5</sup> The recent literatures have proved the basic concepts to realize a simple integration,<sup>3</sup> such as a single transistor,<sup>6</sup> logic circuits,<sup>7</sup> and a ring oscillator<sup>8</sup> utilizing SWNTs as the channel. Among these techniques, a innovative approach<sup>3-5</sup> in realization of complex circuits and high-performance devices was proposed in which perfectly aligned arrays of SWNT on a miscut quartz wafer were used to create SWNT-FETs with a top-gated structure, leading to atomic step-templated growth of the aligned SWNTs. The top-gated aligned array SWNTs show a high integration to synthesize them selectively, and excellent electrical properties for high-performance devices when coupled with atomic layer deposited (ALD) gate oxide or epoxy (SU-8).

In order to improve  $I_{on}/I_{off}$  for the top-gated aligned SWNTs transistor, an electrical burning process<sup>3,4,9</sup> (a selfheating due to application of a drain/source bias in air) is utilized to remove metallic nanotubes selectively. However, these techniques, based on only two terminals (i.e., source and drain), are limited in terms of their ability to monitor and prove the improvement of I<sub>on</sub>/I<sub>off</sub> for transistors in real time, unlike three-terminal devices. On the other hand, the ALD or epoxy gate insulator of the three-terminal device prevents oxygen in the ambient from reaching SWNTs<sup>4,6</sup> during the electrical burning process. As a result, it is difficult to oxidize the metallic SWNTs during the process, resulting in the

survival of numerous metallic nanotubes. Nevertheless, there is no report to date which focuses on the difference in the oxidizing effect when the electrical burning process is executed using the top-gate of the aligned SWNT-FETs.

We report that an electrical burning, based on a local oxidation, in aligned SWNT array FETs can afford a high yield retaining high  $I_{on}/I_{off}$  for a transistor, as compared to the previous two-terminal electrical burning methods swept by only source-drain voltage. In order to demonstrate electrical burning from local oxidation, we build two different structures of parallel aligned SWNT array FETs on quartz substrates. One (reference) has an ALD Al<sub>2</sub>O<sub>3</sub> layer covering the entire SWNT region, such that oxygen-ambient is blocked by the insulator. On the other hand, the ALD  $Al_2O_3$ layer (local oxidation) remains only beneath the top-gate region, which is achieved using a partial etching technique. Electrical burning is performed via self heating by sweeping a high drain/source bias at a gate bias which results in a semiconducting nanotube off-state. Then, a comparison of  $I_d$ - $V_{os}$  curves in the two different devices is performed. Here, the comparison demonstrates that the local oxidation helps to remove metallic nanotubes in air, and high electrical performance of aligned SWNT-FETs after removing metallic SWNTs is observed.

For the generation of the parallel aligned SWNT-FETs with a top-gate on a quartz substrate, the fabrication process is as follows: prior to the growth of the SWNTs, a ST-cut quartz substrate is annealed for 8 h at 900 °C in air. Catalysts, 2-5 Å thick, patterned by a photo process (Shipley 1805 photoresist), are deposited by electron beam deposition of iron ( $\sim 10^{-5}$  torr; Temescal CV-8). The synthesis of the carbon nanotubes in a chemical vapor deposition (CVD) chamber consisted of two steps, a surface pretreatment step and a growth step. The iron catalysts are calcinated in air for  $\sim$ 30 min at 500 °C, and the temperature is ramped up to 900 °C during surface pretreatment (Ar:H<sub>2</sub>=80%:20%). Hydrogen promotes rapid dewetting of the nanoporous film, leading to a dispersed array of discrete catalyst nanoparticles.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: yusuklee@yonsei.ac.kr.

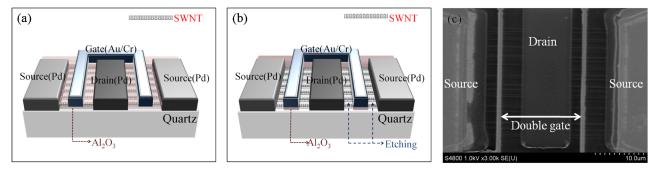

FIG. 1. (Color online) Schematic views of the top-gate aligned array of SWNT-FETs with a 30-nm-thick  $Al_2O_3$  gate insulator: (a) the insulator is covered on the entire SWNTs regions and in the case of (b) the insulator is only beneath the gate region. (c) SEM image of an aligned array of SWNT-FETs, corresponding to (b).

The synthesis of the aligned SWNT array is performed using a flow of H<sub>2</sub>/CH<sub>4</sub>. The grown carbon nanotubes had a diameter of 1-5 nm, with a tube density of four SWNTs/ micrometer. The ALD Al<sub>2</sub>O<sub>3</sub> film is subsequently deposited on the aligned array of SWNTs, utilizing an ASM Microchemistry F-120 ALCVD™ reactor. A 30 nm amorphous Al<sub>2</sub>O<sub>3</sub> film is deposited on the wafer at 300 °C. Using wet etching involving diluted HF solution, the ALD Al<sub>2</sub>O<sub>3</sub> oxide corresponding to the source and drain patterns with spacing of 5  $\mu$ m is removed. Electron beam deposition of Pd is then performed to form source and drain metal contacts in the middle of two catalyst patterns with a spacing of 20  $\mu$ m. Lastly, gate metals are deposited, i.e., Cr/Au (20/100 nm) with a minimum gate length of 1.5  $\mu$ m. Figure 1(a) shows the schematic structure of the aligned SWNTs FET fabricated on a quartz wafer. Local oxidation devices are formed by wet etching (diluted HF solution) from Fig. 1(a); thus, ALD oxide beneath the gate metals remains, while the boundary oxide between the source/drain and gate is finally opened by diluted HF solution, as shown in Fig. 1(b). Figures 1(b) and 1(c) are the schematic diagram and scanning electron microscope (SEM) image of the final structure, respectively.

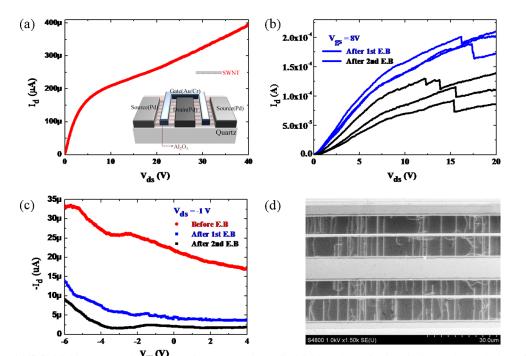

In general, 50% of metallic and 50% of semiconducting carbon nanotubes are randomly grown during the synthesis of SWNTs.<sup>10</sup> As a result, the metallic nanotubes bridged the source and drain, and then degrade  $I_{on}/I_{off}$  in parallel aligned SWNT-FETs arrays. In order to enhance  $I_{on}/I_{off}$  and maintain a high yield of SWNT-FETs, a simple and reliable electrical burning process should be performed to remove the metallic nanotubes from the parallel arrays entirely. However, Fig. 2(a) shows that the parallel aligned SWNTs having a passivated structure [Fig. 1(a)] would not burn at a drain voltage of up to 40 V, as long as a positive gate voltage of 8 V is applied for ensuring turn-off in the semiconducting nanotubes. In order for doing electrical burning at lower voltage, the structure of the parallel aligned SWNTs is modified through etching the boundary oxide between source/drain and gate by diluted HF solution. As a result, the aligned SWNTs are exposed to air, especially oxygen, with the exception of the region beneath the gate, as shown in Figs. 1(b) and 1(c). Using the structure exposed to oxygen, Figs. 2(b)and 2(c) show current-voltage (I-V) curves measured while executing the electrical burning process, where the positive gate voltage is 8 V, such that the positive gate voltage can turn the semiconducting SWNTs off. The current drop of the

FIG. 2. (Color online) (a) I<sub>d</sub>-V<sub>ds</sub> characteristic of the aligned array of SWNT-FETs having the structure shown in Fig. 1(a): electrical breakdown of SWNTs passivated by ALD Al<sub>2</sub>O<sub>3</sub> does not occur up to a drain bias of 40 V. (b) I<sub>d</sub>-V<sub>ds</sub> characteristic of the aligned array of SWNT-FETs having the structure shown in Fig. 1(b): electrical breakdown occurs around 15 V in air. (c) I<sub>d</sub>-V<sub>gs</sub> characteristic of the aligned array of SWNT-FETs of SWNTs having the structure shown in Fig. 1(b), and measured after electrical breakdown occurs, as described in Fig. 2(b). (d) SEM image of a burnt nanotube after the burning and measurement process.

Reuse of AIP Publishing content is solution to the terms at: https://publishing.aip.org/authors/rights-and-permissions. Download to IP: 163.180.186.166 On: Mon, 02 May 2016 06:43:42

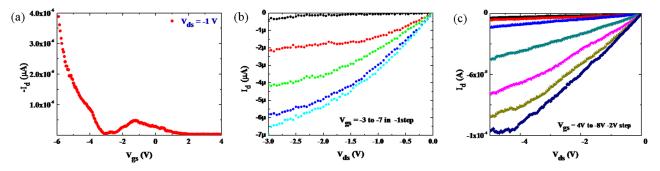

FIG. 3. (Color online) Characteristics of a p-type SWNT-FET with ALD Al<sub>2</sub>O<sub>3</sub> and a width of 10  $\mu$ m [(a) and (b)] and 100  $\mu$ m (c), after electrical burning. (a) Current I<sub>d</sub> vs V<sub>gs</sub> for a 1.5  $\mu$ m gate length SWCNT-FET at V<sub>ds</sub>. (b) Drain current vs drain bias as a function of gate bias. (c) Drain current vs drain bias at a width of 100  $\mu$ m.

blue and black lines, representing sequential electrical breakdown due to the removal of the metallic SWNTs, are observed at a drain/source bias of around 15 V. The sequential burning process can enhance the  $I_{on}/I_{off}$  to 10<sup>3</sup>, i.e., at least two orders of magnitude higher than the original device. Figure 2(d) is the SEM image after the electrical burning procedure. Most electrical breakdown of the metallic SWNTs occurred in the region between the source/drain and gate that the oxygen ambient could be reached.

Here, the difference of  $I_d$ - $V_{ds}$  between Figs. 2(a) and 2(b) should originate from the local oxidizing effect of metallic SWNTs. In the case of the structure of Fig. 1(b), since the electrical burning process is performed in oxygen ambient while applying a gate voltage of 8 V, the current flows mainly through metallic SWNTs. After reaching the saturation region of the current value by sweeping the drain/source bias, the dissipative electrical power affords self-heating of SWNTs, thus heat energy can activate a local oxidation process between the C-C bonds inside metallic SWNTs and oxygen in the air, resulting in the generation of  $CO_2$  gas and the removal of the SWNTs. On the other hand, in case of the passivated SWNT-FETs, shown in Fig. 1(a), it is difficult to perform the local oxidation process during the electrical burning process, since the ALD Al<sub>2</sub>O<sub>3</sub> layer prevents oxygen from reaching the SWNTs;3 thus, the electrical burning process does not occur until the drain/source bias is at least 40 V. With an activated energy and oxygen ambient, the partial etching technique as shown in Fig. 1(b) can contribute to any gate oxide layer, such as  $HfO_2$ ,  $SiO_2$ , and  $SiN_x$ .

Figure 3 shows the transistor characteristics of the aligned SWNTs-FET with a 1.5  $\mu$ m gate length, SWNT-FET with 30-nm-thick Al<sub>2</sub>O<sub>3</sub> and a source/drain width of 10  $\mu$ m [Figs. 3(a) and 3(b)], 100  $\mu$ m [Fig. 3(c)] after metallic nanotubes are removed. The maximum intrinsic transconductance,  $g_m = dI_{ds}/dV_{ds}|_{V_{ds}=-1}$  V of 1.8  $\mu$ S, and a field effect mobility of ~610 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup> are obtained. The device shows a maximum on-current of  $-7 \ \mu A$  at  $V_{ds} = -3 \ V$ and  $V_{gs} = -7$  V. Figure 3(c) shows the I<sub>d</sub>-V<sub>gs</sub> characteristics of an aligned SWNT-FET with a width of 100  $\mu$ m. Following the electrical burning, the channel contains approximately 15 aligned SWNTs. A recent report<sup>4</sup> shows the average per tube mobility, denoted as  $\langle \mu t \rangle = (L/WC_tD_s)(1/V_d)$  $\times (\partial I_{ds} / V_g)$ , where C<sub>t</sub> is the capacitance per unit length for a semiconducting tube in the array, L is a gate length, and D<sub>s</sub> is the density of the semiconducting nanotube spanning the channel. The field effect mobility of an aligned array of SWNT-FETs with 100  $\mu$ m source/drain width was found to be 2890 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>. The maximum on-current is ~-100  $\mu$ A at V<sub>ds</sub>=-4 V and V<sub>gs</sub>=-8 V, as shown in Fig. 3(c).

In conclusion, we fabricate SWNT-FETs in a 1.5  $\mu m$ gate length with a 30 nm thick ALD with/without an opening window allowing oxygen to reach SWNT-FETs. Using these structures, the electrical burning process with/without an oxygen-ambient is evaluated in terms of monitoring and improving I<sub>on</sub>/I<sub>off</sub> for transistors in real time. After the electrical burning process is performed,  $I_{\rm on}/I_{\rm off}$  for the transistor increased by two orders relative to the original device, and the maximum intrinsic transconductance=1.8  $\mu$ S, the field effect mobility  $\sim 610 \text{ cm}^2 \text{ V}^{-1} \text{ S}^{-1}$ , the maximum on-current  $\sim$ -7  $\mu$ A at V<sub>ds</sub>=-3 V, and V<sub>gs</sub>=-7 V is achieved when three semiconducting SWNTs with 10  $\mu$ m source/drain width are used for the measurement. Furthermore, the field effect mobility and the maximum on-current of the aligned array of the SWNT-FETs 100 µm source/drain width are 2890 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup> and  $\sim$ -100  $\mu$ A at V<sub>ds</sub>=-4 V and V<sub>gs</sub> =-8 V, respectively. These results suggest opportunities for manufacturing integrated circuits using aligned single-walled nanotubes arrays with high yield.

This research was supported in part by the National Research Foundation of Korea (NRF) under Grant Nos. 2009-0068841, 2010-0013619, and KRF-2007-313-D00963.

- <sup>2</sup>P. Qi, O. Vermesh, M. Grecu, A. Javey, Q. Wang, and H. Dai, Nano Lett. **3**, 347 (2003).

- <sup>3</sup>S. Kim, S. H. Ju, J. H. Back, S. M. Shim, D. B. Janes, and S. Mohammadi, Adv. Mater. **21**, 564 (2009).

- <sup>4</sup>S. J. Kang, C. Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, S. V. Rotkin, and J. A. Rogers, Nat. Nanotechnol. 2, 230 (2007).

- <sup>5</sup>C. Kocabas, S. J. Kang, T. Ozel, M. Shim, and J. A. Rogers, J. Phys. Chem. C 111, 17879 (2007).

- <sup>6</sup>S. Kim, Y. Xuan, J. H. Back, P. D. Ye, M. S. Shim, and S. Mohammadi, Appl. Phys. Lett. **90**, 163108 (2007).

- <sup>7</sup>A. Javey, H. Kim, M. Brink, W. Qian, A. Ural, G. Jing, P. McIntyre, P. McEuen, M. Lundstrom, and H. Dai, Nature Mater. **1**, 241 (2002).

- <sup>8</sup>Z. Chen, J. Appenzeller, Y. Lin, J. S. Oakley, A. G. Rinzler, J. Tang, S. J.

- Wind, P. M. Solomon, and P. Avouris, Science 311, 1735 (2006).

<sup>9</sup>Y. Feng, K. Lee, H. Farhat, and J. Kong, J. Appl. Phys. 106, 104505

- (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009). (2009

<sup>10</sup>Y. Zhou, A. Gaur, S. H. Hur, C. Kocabas, M. A. Meitl, M. Shim, and J. A. Rogers, Nano Lett. **4**, 2031 (2004).

<sup>&</sup>lt;sup>1</sup>A. Javey, G. Jing, W. Qian, M. Lundstrom, and D. Hongjie, Nature **424**, 654 (2003).