# High-temperature Electrical Behavior of a 2D Multilayered MoS<sub>2</sub> Transistor

Yeonsung LEE, Heekyeong PARK, Junyeon KWON, Omkaram INTURU and Sunkook KIM<sup>\*</sup> Department of Electronics and Radio Engineering, Kyung Hee University, Yongin 446-701, Korea

(Received 23 December 2013, in final form 27 January 2014)

This paper reports the high-temperature-dependent electrical behavior of a 2D multilayer  $MoS_2$  transistor. The existence of a big Schottky barrier at the  $MoS_2$ -Ti junction can reduce carrier transport and lead to a lower transistor conductance. At a high temperature (380 K), the field-effect mobility of the multilayer  $MoS_2$  transistor increases to  $16.9 \text{ cm}^2 \text{V}^{-1} \text{sec}^{-1}$ , which is 2 times higher than the value at room temperature. These results demonstrate that at high temperature, carrier transport in a  $MoS_2$  with a high Schottky barrier is mainly affected by thermionic emission over the energy barrier.

PACS numbers: 42.30.R, 42.40.Ht, 42.30.Kq

Keywords: 2D layered semiconductor,  $MoS_2$ , High temperature, Thermionic emission, Thin film transistor DOI: 10.3938/jkps.64.945

## I. INTRODUCTION

For future display technologies, there are strong demands to provide high-resolution and mechanicallyflexible flat panels, and significant progress has recently been achieved in improving high-performance flexible and foldable organic light-emitting diode (OLED) displays [1,2]. A conventional display consists of two major systems: a backplane to drive the OLED display device and address active-matrix pixels and a display device to create display images and movies. Sustained efforts to realize flexible backplanes have been reported for flexible and conformable thin-film transistors (TFTs), a core device to drive/switch active matrix display pixels [3–5]. However, conventional thin-film materials such as amorphous Si ( $\alpha$ -Si), low-temperature poly Si (LTPS), and oxides, limit the use of such TFTs in flexible backplanecircuitry due to their fragility and relatively low mobility.

Two-dimensional (2D) layered semiconducting chalcogenides (such as  $MoS_2$ ,  $MoSe_2$ ,  $WS_2$ ,  $WSe_2$ , etc.) have attracted much attention due to their having an intrinsically high carrier mobility (> 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), mechanical flexibility for a 2D layered structure, and a finite bandgap (~1.35 eV) [6–8]. For a high-performance 2D layered semiconducting transistor, recent reports suggest that Ti was selected from among the low work function materials because its favorable interface geometry Ti allows bonding and the electronic density of states (DOS) at the Fermi level to be maximized through an increase in the overlap between the states at the interface [9]. However, such improvements for the transistors to date have fundamentally been hampered by the presence of a Schottky barrier at the 2D layered MoS<sub>2</sub>-Ti metal junction. A natural bulk MoS<sub>2</sub> crystal (SPI supplies, USA) is typically found in the '2H phase', what has a semiconducting property, but often contains the '3R phase', what shows a semi-metallic behavior [10]. This is because of the doping concentration and the chirality in the natural MoS<sub>2</sub> crystal, which can not to be controlled exactly. Previous reports on MoS<sub>2</sub> transistors show outstanding electrical properties, including high performance and a low subthreshold slope [4], but some of those devices fabricated till to date have contained a high Schottky barrier at the MoS<sub>2</sub>-Ti metal junction after H<sub>2</sub> annealing, and the presence of the Schottky barriers severely blocks carrier transport in the channel and limits the transistor performance matrix.

In this research, we investigated the high-temperature electrical behavior of a  $MoS_2$  transistor with a high Schottky barrier. From experimental temperaturedependent current-voltage (IV) measurements, the extracted field-effect mobility of the  $MoS_2$  transistor was found to be proportional to the temperature. The carrier mobility in a typical  $MoS_2$  crystal is limited by optical phonon scattering at high temperature, but the present immature  $MoS_2$  transistors, as opposed to ohmically $contacted MoS_2$  transistors, show an enhanced mobility at high temperature. High temperature leads to a larger thermionic emission that transports electrons over the energy barrier. Furthermore, the carrier transport mechanism and the calculation of Schottky barrier in the multilayer  $MoS_2$  devices are discussed based on the observations.

<sup>\*</sup>E-mail: Seonkuk@khu.ac.kr; Fax: +82-31-201-3486

-L946-

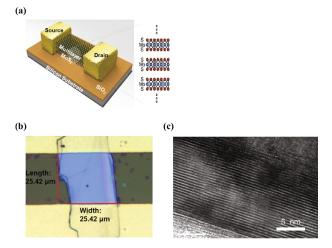

Fig. 1. (Color online) (a) Schematic diagram of a 2D multilayered  $MoS_2$  TFT with a back-gated structure. (b) Optical microscope image of this device. (c) Bright-field TEM image of the layered structure. A monolayer generally has a thickness of 1nm.

# II. MULTILAYER MOS<sub>2</sub> TRANSISTOR AND ELECTRICAL CHARACTERISTICS

Figure 1(a) shows a cross-sectional view of a 2D multilayered  $MoS_2$  transistor with a back-gated structure, where a highly-*p*-doped Si wafer (resistivity  $< 5 \times 10^{-3}$  $\Omega \cdot cm$ ) is utilized as a common back and is covered with a 300-nm-thick  $SiO_2$  layer as a gate dielectric. The fabrication begins with mechanical exfoliation of the  $MoS_2$ layers from bulk  $MoS_2$  crystals (SPI supplies, USA), and then transfers them onto a thermally-grown  $SiO_2$  layer. After the mechanical exfoliation of a multilayer MoS<sub>2</sub> crystal, the sample is annealed in a vacuum tube at 200  $^{\circ}$ C for 2 hours (100 sccm Ar and 10 sccm H<sub>2</sub>) to remove the tape residue on the surface of the  $MoS_2$  and to lower the contact resistance in the MoS<sub>2</sub>-Ti/Au junction. Finally, Ti/Au (20 nm/300 nm) metals for S-D electrodes are deposited by using e-beam evaporation and are patterned by using photolithography, with a channel length of 11.47  $\mu$ m. Figure 1(c) shows the bright-field transmission electron microscopy (TEM) image of the layer-bylayer structure, where each layer is weakly held together by Van der Waals interactions.

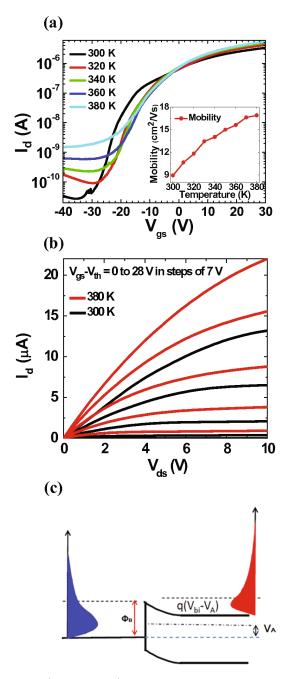

First, the electrical characteristics of an as-fabricated MoS<sub>2</sub> TFT were measured at room temperature. Figure 2(a) shows the drain current versus gate-source voltage  $(I_d-V_{gs})$  of this device at a drain voltage Vds = 1 V. The MoS<sub>2</sub> transistor exhibits the on/off current ratio  $(I_{on}/I_{off}) \sim = 10^6$  and a threshold voltage  $V_{th} = -11$  V. The field-effect mobility ( $\mu$ m) deduced from the maximum transconductance ( $g_m = dI_d / dV_{gs}$  at  $V_{ds} = 1$  V) of 0.1  $\mu$ S is 8.93 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature. Figure 2(b) shows typical output characteristics ( $I_d-V_{ds}$ ) under various gate voltages in steps of 7 V for the multi-layer MoS<sub>2</sub>. The  $I_d-V_{ds}$  curves are close to those of a con-

Fig. 2. (Color online) Measured electrical characteristics of a depletion-mode *n*-type MoS<sub>2</sub> transistor at room temperature: (a) drain current versus drain bias (output curve) with respect to gate bias, and (b) drain current versus gate-source voltage at  $V_{ds} = 1$  V on a log scale and a linear scale.

ventional *n*-channel metal oxide semiconductor (NMOS) transistor, having a linear triode region at low  $V_{ds}$  and a saturation region at high  $V_{ds}$ . The drain current at high  $V_{ds}$  is observed to fully saturate for all gate voltages.

## III. TEMPERATURE DEPENDENT IV CHARACTERISTICS OF A MOS<sub>2</sub> TRANSISTOR

To investigate the temperature-dependent carrier transport mechanism, we measured the electrical characteristics of the device as a function of temperature (300 to 380 K), as shown in Fig. 3. The carrier mobility is intrinsically determined by the scattering mechanism, such as scattering from the Schottky barrier and from, ionized impurities and optical phonon scattering. Our reported result demonstrates that for a well-designed  $MoS_2$  transistor, having a relatively low Schottky barrier, the scattering mechanism is dominated by enhanced

Fig. 3. (Color online) Electrical characteristics of a 2D multilayer MoS<sub>2</sub> transistor for various temperatures. (a) The  $I_d$ - $V_{gs}$  characteristics of a representative device. The inset shows the temperature-dependent field-effect mobility at temperatures from 300 K to 380 K in steps of 10 K. (b)  $I_d$ - $V_{gs}$  characteristics for  $V_{gs}$ - $V_{th}$  at room temperature (black line) and high temperature of 380 K (red line). (c) Energy band diagram and carrier distribution at the Schottky barrier between the MoS<sub>2</sub> semiconductor and the Ti/Au metal.

optical-phonon and acoustic- phonon scattering above room temperature. Thus, the extracted field-effect mobility of a good device should be inversely proportional to the temperature. However, the mobility behavior of the device (Fig. 3(a)) is fully contradictory with that of the previous good device; the mobility of the present MoS<sub>2</sub> transistor ( $\mu$ m < 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) is proportional to the temperature. At high temperature, the lattice vibration limits the carrier mobility at the ohmically-contacted 2D MoS<sub>2</sub> transistor, but the transport of electrons on this device is strongly limited by the thermionic emission over the potential barrier due to the large Schottky barrier ( $\Phi_B$ ) at MoS<sub>2</sub>-Ti/Au junction. The current due to thermionic emission in a representative MoS<sub>2</sub> transistor, as shown in Fig. 3(c), is given by

$$J_T = A * T^2 * e^{\frac{-q\Phi_B}{kT}} [e^{\frac{qV_A}{kT}} - 1],$$

(1)

where  $\Phi_B$  is the Schottky barrier height,  $V_A$  is an applied bias, and the parameter A is the effective Richardson constant. The above equation shows that the probability of carriers going over the potential barrier is enormously increased as the temperature is increased, thus, a larger total current  $(J_T)$  leads to a higher mobility at higher temperatures. The carrier transport in the present transistor with a high Schottky barrier is strongly limited by thermionic emission; thus, the mobility at high temperature (380 K) is increased to 16.9 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, which is 2 times higher than that at room temperature.

## **IV. CONCLUSION**

In conclusion, the high-temperature-dependent carrier transport of a MoS<sub>2</sub> transistor with a high contact resistance is investigated. By comparing the transistor is mobility with increasing operation temperature, we found the  $\mu$ m to be limited by thermionic emission at high operation temperature due to the high Schottky barrier at the MoS<sub>2</sub>-Ti/Au metal junction. In this regards, a high-performance 2D multilayer MoS<sub>2</sub> transistor having a zero or slightly negative Schottky barrier can be realized. Furthermore, the observing the high-temperature electrical behavior will be a good method for determining whether the device is an ohmically-contacted or a large-Schottky-barrier device.

### ACKNOWLEDGMENTS

This research was supported by a grant (20120560) from Kyung Hee University and by the Industrial Strategic Technology Development Program (10045145).

#### REFERENCES

S. Kim, H. J. Kwon, S. Lee, H. Shim, Y. Chun, W. Choi, J. Kwack, D. Han, M. Song, S. Kim, S. Mohammadi, I. Kee and S. Y. Lee, Adv. Mater. 23, 3511 (2011) -L948-

- [2] H. Sasabe, J. I. Takamatsu, T. Motoyama, S. Watanabe, G. Wagenblast, N. Langer, O. Molt, E. Fuchs, C. Lennartz and J. Kido, Adv. Mater. 22, 5003 (2010)

- [3] Q. Cao, H. S. Kim, N. Pimparkar, J. P. Kulkarni, C. Wang, M. Shim, K. Roy, M. A. Alam and J. A. Rogers, Nature. 454, 495 (2008)

- [4] S. Kim, A. Konar, W. S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J. B. Yoo, J. Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi and K. Kim, Nat. Commun. 3, 1011 (2012)

- [5] J. Lee, D. H. Kim, J. Y. Kim, B. Yoo, J. W. Chung, J. I. Park, B. L. Lee, J. Y. Jung, J. S. Park, B. Koo, S. Im, J. W. Kim, B. Song, M. H. Jung, J. E. Jang, Y. W. Jin

and S. Y. Lee, Adv. Mater. 25, 5886 (2013)

- [6] W. Choi, M. Y. Cho, A. Konar, J. H. Lee, G. B. Cha, S. C. Hong, S. Kim, J. Kim, D. Jena, J. Joo and S. Kim, Adv. Mater. 24, 5832 (2012)

- [7] RadisavljevicB, RadenovicA, BrivioJ, GiacomettiV and KisA, Nat Nano. 6, 147 (2011)

- [8] J. Pu, Y. Yomogida, K. K. Liu, L. J. Li, Y. Iwasa and T. Takenobu, Nano Letters. **12**, 4013 (2012)

- [9] K. F. Mak, C. Lee, J. Hone, J. Shan and T. F. Heinz, Physical Review Letters. 105, 136805 (2010)

- [10] M. Chhowalla, H. S. Shin, G. Eda, L. J. Li, K. P. Loh and H. Zhang, Nat Chem. 5, 263 (2013)