## Nanowire-based ternary transistor by threshold-voltage manipulation

Junebeom Han, Taekyung Lim, Jihye Bong, Keumyoung Seo, Sunkook Kim, and Sanghyun Ju

Citation: Applied Physics Letters **104**, 143509 (2014); doi: 10.1063/1.4871413 View online: http://dx.doi.org/10.1063/1.4871413 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/104/14?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Current-voltage spectroscopy of dopant-induced quantum-dots in heavily n-doped junctionless nanowire transistors Appl. Phys. Lett. **104**, 133509 (2014); 10.1063/1.4870512

Appl. 1 Hys. Lett. 104, 133303 (2014), 10.1003/1.4070312

Short channel mobility analysis of SiGe nanowire p-type field effect transistors: Origins of the strain induced performance improvement Appl. Phys. Lett. **101**, 143502 (2012); 10.1063/1.4756910

Modeling of threshold voltage, mobility, drain current and subthreshold leakage current in virgin and irradiated silicon-on-insulator fin-shaped field effect transistor device J. Appl. Phys. **109**, 084504 (2011); 10.1063/1.3553836

Bandgap shift by quantum confinement effect in 100 Si-nanowires derived from threshold-voltage shift of fabricated metal-oxide-semiconductor field effect transistors and theoretical calculations J. Appl. Phys. **109**, 064312 (2011); 10.1063/1.3559265

Ambient field effects on the current-voltage characteristics of nanowire field effect transistors Appl. Phys. Lett. **98**, 063508 (2011); 10.1063/1.3555426

## AP Journal of Applied Physics

*Journal of Applied Physics* is pleased to announce André Anders as its new Editor-in-Chief

## Nanowire-based ternary transistor by threshold-voltage manipulation

Junebeom Han,<sup>1</sup> Taekyung Lim,<sup>1</sup> Jihye Bong,<sup>1</sup> Keumyoung Seo,<sup>1</sup> Sunkook Kim,<sup>2</sup> and Sanghyun Ju<sup>1,a)</sup>

<sup>1</sup>Department of Physics, Kyonggi University, Suwon, Gyeonggi-Do 443-760, South Korea

<sup>2</sup>Department of Electronics and Radio Engineering, Kyung Hee University, Yongin, Gyeonggi-Do 446-701, South Korea

(Received 25 November 2013; accepted 3 April 2014; published online 10 April 2014)

We report on a ternary device consisting of two nanowire channels that have different threshold voltage (V<sub>th</sub>) values and show that three current stages can be produced. A microscale laser-beam shot was utilized to selectively anneal the nanowire channel area to be processed, and the amount of V<sub>th</sub> shift could be controlled by adjusting the laser wavelength. Microscale laser annealing process could control V<sub>th</sub> of the individual nanowire transistors while maintaining the other parameters the constant, such as the subthreshold slope, on–off current ratio, and mobility. This result could provide a potential for highly integrated and high-speed ternary circuits. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4871413]

Integrating high-density electronic circuits, increasing computational efficiency, and reducing the device size are critical requirements for developing existing and future electronics. In this sense, multivalued logic circuits, especially ternary devices, are proposed to solve the above issues. In contrast to binary logic circuits currently used in all electronic circuitry, ternary logic circuits could contribute to the increase in the degree of integration of the devices by decreasing the number of devices that make up the logic blocks.<sup>1–4</sup> The decrease in the number of devices may reduce the parasitic effect and consequently increase tolerance to noise. Moreover, data processing can be accelerated because ternary logic circuits could process a large volume of data in a short time. Considering these advantages, ternary logic circuits should be considered as one of the most important research topics in the investigation of next-generation complementary metal-oxide semiconductor circuits.

To fabricate ternary devices, the operating voltages must be categorized into three levels. One of the fabrication methods of ternary devices involves the use of two semiconductor channels. Because the threshold voltage (V<sub>th</sub>) values of the two semiconductor channels must be different from each other, V<sub>th</sub> must be capable of being selectively shifted to only one semiconductor channel. In addition, a method should be developed to accurately produce a positive shift in V<sub>th</sub> according to the original design plan. Furthermore, only V<sub>th</sub> should be shifted while the other transistor characteristics must be maintained constant, such as the on-current (Ion), subthreshold slope (SS), on-off current ratio (I<sub>on</sub>/I<sub>off</sub>), and field-effect mobility ( $\mu_{eff}$ ). Many studies have been conducted so far to control Vth. In some previous studies, thermal annealing, ultraviolet (UV), UV-ozone (UVO), and plasma treatments were implemented to control V<sub>th</sub>.<sup>5-8</sup> Moreover, excimer and femtosecond lasers were used to achieve V<sub>th</sub> control.<sup>9,10</sup> However, two major limitations were encountered in these approaches: (i) the other transistor characteristics such as  $I_{on}$ , SS,  $I_{on}/I_{off}$ , and  $\mu_{eff}$  changed along with the change in  $V_{th}$  after the processes, and (ii) a selective transistor characteristic change in only the semiconducting channel could not be achieved, because some of the methods should be employed to the entire substrate. Thus, these methods are not sufficient to fabricate ternary devices.

In this study, a selective laser anneal on a nanowire channel was implemented to control the  $V_{th}$  shift. The amount of change in  $V_{th}$  of a SnO<sub>2</sub> nanowire transistor was investigated by varying the laser wavelength. The semiconducting nanowires could have different  $V_{th}$  values by using a micro-scale laser annealing process. Using our proposed method, we fabricated a ternary device which showed three current stages.

A ternary device consisting of two bottom-gate structural transistors was fabricated using a SnO<sub>2</sub> nanowire as a semiconductor channel and an atomic layer-deposited Al<sub>2</sub>O<sub>3</sub> ( $T_{ox} = 30$  and 70 nm) as a gate insulator. The SnO<sub>2</sub> nanowires with band gap ( $E_g$ ) of ~3.6 eV at 300 K were synthesized by chemical vapor deposition.<sup>11</sup> The average diameter and length of the SnO<sub>2</sub> nanowires were 30 nm and over 10  $\mu$ m, respectively. The gate and source–drain electrodes were formed using a sputtered ITO thin film (100 nm) by a lift-off process.

A pulsed Nd:YAG laser (Surelite III-10, Continuum, Inc.) was operated at two different wavelengths (266 and 532 nm). The laser annealing process was performed in ambient air. The laser was exposed only to the nanowire channel region using a microlevel laser shot system. The nanowire channel area could be observed through a microscope in the laser shot system during the laser annealing process, and the target exposed position and beam spot size  $(2-8 \ \mu m)$  could be adjusted using a micro-xyz stage.

The transistor characteristics were measured using a semiconductor parameter analyzer (Agilent B1500A).  $\mu_{eff}$  was derived from the calculated gate-to-channel capacitance  $C_i = 2\pi\epsilon_0 k_{eff} L/\cosh^{-1}(1 + t_{ox}/r)$  using  $\mu_{eff} = dI_{ds}/dV_{gs} \times L^2/C_i \times 1/V_{ds}$ . The effective dielectric constant of Al<sub>2</sub>O<sub>3</sub> ( $k_{eff}$ ), the channel length (*L*), and the radius (*r*) of the SnO<sub>2</sub> nanowire were 9.0, 2.4  $\mu$ m, and 15 nm, respectively. The statistical data of the devices were calculated from the

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: shju@kgu.ac.kr.

measured transistor characteristics in terms of V<sub>th</sub> (V<sub>gs</sub> at  $I_{ds} = 10 \text{ nA}$  and  $V_{ds} = 1.0 \text{ V}$ ),  $I_{on}$  ( $I_{ds}$  at  $V_{gs} = V_{th} + 2 \text{ V}$  and  $V_{ds} = 1.0 \text{ V}$ ), and off-current ( $I_{off}$  at  $V_{ds} = 1.0 \text{ V}$ ) and average  $I_{ds}$  of the five-point  $I_{ds}$  from the off-region).

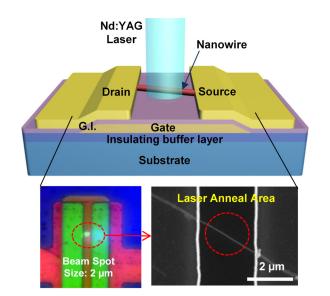

Figure 1 shows the schematic diagram of the laser annealing on the SnO<sub>2</sub> nanowire channel area in the bottom-gate nanowire transistor. The insets in Fig. 1 show the microscope image, which was obtained during a laser shot, and the field emission scanning electron microscope (FE-SEM) image of the nanowire channel region. The length and diameter of the single SnO2 nanowire between the source–drain electrodes were  $\sim 2.4 \,\mu m$  and  $\sim 30 \,nm$ , respectively. Two different laser wavelengths (266 and 532 nm) with laser fluence values of 0.34 and 0.12 J/cm<sup>2</sup>, respectively, and a 2-s exposure time were employed. The beam spot diameter was  $\sim 2.0 \,\mu\text{m}$ . The unique aspect of the selective laser annealing process is that the laser can be directed only on the nanowire channel region without affecting the other areas, especially the nanowire source-drain contact areas. Typical thermal treatment or plasma treatment may produce undesirable effects because it is applied to the entire substrate. In addition, because thermal treatment is performed at 400–900 °C for 30–120 min, the method cannot be used for devices that must be fabricated on plastic substrates. However, the selective laser annealing process employed in our study provides a solution to the above problems on the basis of its advantages: the annealing treatment can be carried out for only the targeted areas in a selective manner, and laser illumination for a short period of time reduces the process time and minimizes any possible thermal damage to the substrate.

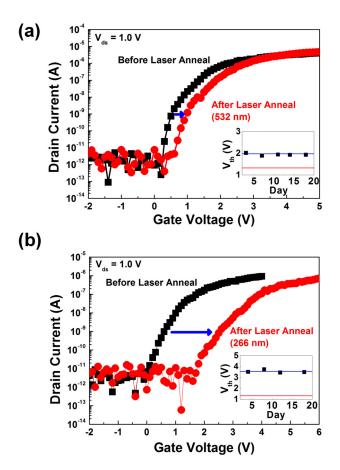

The log-scale drain current versus gate–source voltage  $(I_{ds}-V_{gs})$  characteristics of the single SnO<sub>2</sub> nanowire transistor at  $V_{ds} = 1.0$  V before (black square) and after (red circle) laser annealing at two wavelengths (266 and 532 nm) are

FIG. 1. Schematic diagram of a single SnO<sub>2</sub> nanowire transistor. The channel region of the nanowire was exposed to a pulsed Nd:YAG laser (laser fluence:  $\sim 0.34 \text{ J/cm}^2$  (266 nm) and  $0.12 \text{ J/cm}^2$  (532 nm)). The inset shows the top view of the microscopic image of the device area with a laser shot on only the nanowire channel region. The laser spot size was 2  $\mu$ m. The other inset shows the FE-SEM image of the nanowire channel region. The scale bar is 2.0  $\mu$ m.

shown in Fig. 2. Figure 2(a) shows the representative  $I_{ds}$ - $V_{gs}$ characteristics of the SnO<sub>2</sub> nanowire transistor under a 532-nm laser annealing process with a laser fluence of  $0.12 \text{ J/cm}^2$  and an exposure time of 2 s. Before laser annealing, the SnO<sub>2</sub> nanowire transistor exhibited  $V_{th} = 1.34 \text{ V}$ , SS = 0.5 V/dec,  $I_{on}/I_{off} = 3.26 \times 10^6$ ,  $I_{on} = 2.31 \times 10^{-6} A$ , and  $\mu_{\rm eff} = 14\ 0.89\ {\rm cm}^2/{\rm V}\cdot{\rm s}$ . After laser annealing, the same device showed a positively shifted  $V_{th} = 2.10 \text{ V}$  while maintaining similar values—SS = 0.5 V/dec,  $I_{on}/I_{off} = 2.73 \times 10^6$ ,  $I_{on} = 3.47 \times 10^{-6} \text{ A}$ , and  $\mu_{eff} = 15\ 004\ \text{cm}^2/\text{V}$  s. Figure 2(b) shows the representative  $I_{ds}$ - $V_{gs}$  characteristics of the SnO<sub>2</sub> nanowire transistor under a 266-nm laser annealing process with a laser fluence of  $0.34 \text{ J/cm}^2$  and an exposure time of 2 s. The as-fabricated SnO2 nanowire transistor showed  $V_{th} = 1.32 \text{ V}, \text{ SS} = 0.7 \text{ V/dec}, I_{on}/I_{off} = 1.31 \times 10^6, I_{on} = 6.25$  $\times 10^{-7}$  A, and  $\mu_{eff} = 3378$  cm<sup>2</sup>/V·s; whereas the SnO<sub>2</sub> nanowire transistor treated with laser annealing exhibited a positively shifted  $V_{th} = 3.52 V$  while maintaining similar values of SS = 0.8 V/dec,  $I_{on}/I_{off} = 1.21 \times 10^6$ ,  $I_{on} = 5.03 \times 10^{-7} \text{ A}$ , and  $\mu_{\rm eff} = 3589 \text{ cm}^2/\text{V} \cdot \text{s}$ . As a result, the V<sub>th</sub> showed a positive shift of 0.76 V (532 nm) and 2.20 V (266 nm) without any major changes in the SS,  $I_{on}/I_{off}$ , and  $I_{on}$  values.

In the case of the oxide nanowire transistors, thermal annealing, UV, UVO, or plasma treatment produces a negative or positive  $V_{th}$  shift.<sup>5-10</sup> Moreover, some treatment processes could restore  $V_{th}$  to its original state. In this context, we verified in this study whether the  $V_{th}$  characteristic can

FIG. 2. (a)  $I_{ds}-V_{gs}$  characteristics of the SnO<sub>2</sub> nanowire transistor before and after the laser annealing process (532 nm). (b)  $I_{ds}-V_{gs}$  characteristics of the SnO<sub>2</sub> nanowire transistor before and after the laser annealing process (266 nm).

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP

be maintained or restored after the laser annealing process. The insets in Figs. 2(a) and 2(b) show the change in the transistor characteristics after a lapse of time after laser annealing. As shown in the figures, the transistor characteristics remained the same even after 18 days.

The most prominent effect of laser annealing is the control of the V<sub>th</sub> shift by adjusting the laser wavelength. The V<sub>th</sub> shift after the 532-nm laser annealing process exhibited a small change, but it displayed a large change after the 266-nm laser annealing process. On the other hand, the unchanged transistor characteristics-i.e., SS, Ion/Ioff, and I<sub>on</sub>—after laser annealing indicated that the laser annealing process did not cause degradation in the nanowire at the interface states. In other words, the surface states in the nanowires did not increase during laser annealing. There are several methods to improve the SS of an oxide nanowire transistor: (i) reducing the thickness of the gate insulator,<sup>12</sup> (ii) using the gate insulator which has a high dielectric constant,<sup>12</sup> and (iii) controlling the interface between gate insulator and semiconductor nanowire channel.<sup>7,13</sup> On the other hand, only the V<sub>th</sub> shifted without degrading the other transistor characteristics following the decrease in the oxygen vacancies  $(V_o, V_o^+, \text{ and } V_o^{++})$ .<sup>14,15</sup> The laser anneal, which was applied in this study, was exposed only on nanowire channel surface in ambient air. The oxygen ions generated from the laser annealing process in ambient air then filled the oxygen vacancies and reduced the final amount of Vo. Because  $V_o$ ,  $V_o^+$ , and  $V_o^{++}$  play the role of electrontrapping sites, a decrease in such sites leads to a positive V<sub>th</sub> shift in the N-type oxide nanowire transistors.<sup>16</sup> The laser anneal process could change the amount of oxygen vacancies on nanowires, but might not affect the interface state between gate insulator and nanowire. For this reason, V<sub>th</sub> of the device was shifted without changing SS.

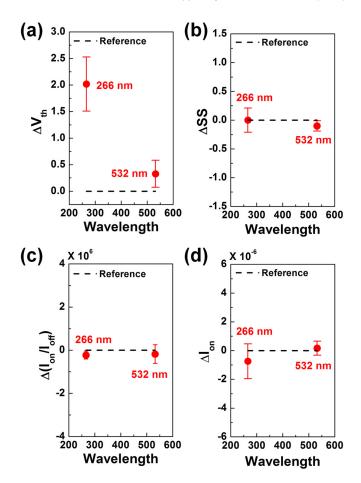

The changes in  $V_{th}$ , SS,  $I_{on}/I_{off}$ , and  $I_{on}$  in the SnO<sub>2</sub> nanowire transistors in six devices before and after laser annealing were measured, and the average and standard deviations are shown in Fig. 3. After laser annealing at 266 nm,  $V_{th}$  showed a positive shift of  $2.02 \pm 0.51$  V. On the other hand, laser annealing at 532 nm produced only a positive shift of  $0.33 \pm 0.25$  V, which was a relatively slight change. Thus, the decrease in the wavelength led to the increase in the amount of positive shift. We assume that this phenomenon occurred because the lower wavelength (266 nm and 4.66 eV) of the laser reacted more actively with the surface of the  $SnO_2$  nanowire (bandgap of 3.6 eV) in ambient air than the higher wavelength (532 nm and 2.33 eV), consequently filling up the oxygen vacancies with oxygen. Meanwhile, the SS, Ion/Ioff, and Ion values showed no significant changes after laser annealing at the two laser wavelengths (266 and 532 nm). The  $SnO_2$  nanowire transistors after laser annealing exhibited unchanged average values of  $\Delta$ SS (0.00 ± 0.21 V/dec (266 nm) and  $-0.10 \pm 0.09$  V/dec (532 nm)),  $\Delta(I_{on}/I_{off})$  ((-0.23 ± 0.19) × 10<sup>6</sup> (266 nm) and  $(-0.18 \pm 0.43) \times 10^{6} (532 \text{ nm}))$ , and  $\Delta I_{on} = ((-0.74 \pm 1.21))$  $\times 10^{-6}$  A (266 nm) and (0.17  $\pm$  0.49)  $\times 10^{-6}$  A (532 nm)). Note that deviation ( $\Delta$ ) is the difference between the unannealed value and the annealed value.

As an application of our capability to adjust the  $V_{th}$  values of individual SnO<sub>2</sub> nanowires, we fabricated a ternary

FIG. 3. Variations in the (a) threshold voltage, (b) subthreshold slope, (c) on–off current ratio, and (d) field-effect mobility of the  $SnO_2$  nanowire transistors after the laser annealing process at different wavelengths (266 and 532 nm).

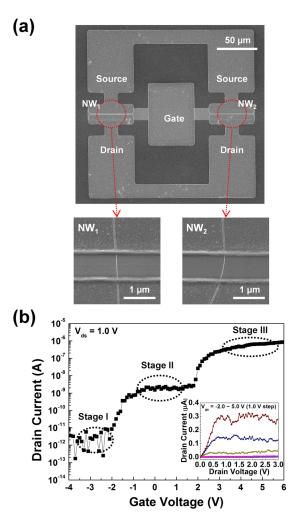

device. Two methods are available to encode and operate the ternary devices using ternary variables: (i) unbalanced ternary encoding with three values [0, 1, and 2] of the ternary variable, and (ii) balanced ternary encoding with three values [-1, 0, and 1] of the ternary variable. Nd:YAG laser annealing with a microscale beam spot size introduced here appears to be the ideal method for fabricating the ternary transistor to control  $V_{th}$ . Figure 4(a) shows the FE-SEM image of the representative ternary device consisting of two SnO<sub>2</sub> nanowire channels with different V<sub>th</sub> and I<sub>on</sub> values. Nd:YAG laser annealing (266 nm and 0.34 J/cm<sup>2</sup>) for 2 s was carried out in only one nanowire channel (NW<sub>2</sub>) out of the two nanowire channels (NW<sub>1</sub> and NW<sub>2</sub>). As a result, the laser-annealed device showed a V<sub>th</sub> of 3.0 V whereas the other nanowire transistor that did not undergo laser annealing showed a V<sub>th</sub> of 0.1 V. The laser anneal method which was introduced in this study can only manipulate Vth. Thus, Ion level should be controlled by changing the thicknesses of gate insulators on unannealed and annealed nanowire channel regions. The 70-nm-thick and 30-nm-thick Al<sub>2</sub>O<sub>3</sub> thin films were utilized on the unannealed and annealed transistors, respectively. The nanowire with the low Ion was selected on the unannealed channel region and the nanowire with the high Ion was treated with the laser anneal.

Figure 4(b) shows the log-scale  $I_{ds}$ - $V_{gs}$  of the ternary device. The two transistor characteristics with different  $V_{th}$

FIG. 4. Ternary device. (a) FE-SEM image of the ternary device based on two n-type  $\text{SnO}_2$  nanowire transistors. The scale bar is  $100 \,\mu\text{m}$ . The inset shows the representative nanowire channel regions of the transistors; the scale bar is  $10 \,\mu\text{m}$ . (b)  $I_{ds}$ – $V_{gs}$  characteristics of the ternary device. The inset shows  $I_{ds}$ – $V_{ds}$  characteristics of the ternary device.

values combined to exhibit a device characteristic with three current levels. In other words, three different current stages of ~3 × 10<sup>-12</sup> A (stage I), ~1.5 × 10<sup>-9</sup> A (stage II), and ~6 × 10<sup>-6</sup> A (stage III) exist at below -2 V, from -1.1 to 1.8 V, and over 2.8 V, respectively. The inset in Fig. 4(b) shows the drain current versus drain-to-source voltage (I<sub>ds</sub>-V<sub>ds</sub>) characteristics of a representative ternary device with a V<sub>gs</sub> range from -2.0 to 5.0 V in 1.0 V steps and after laser annealing. One current group had a value of ~4 nA at V<sub>ds</sub> = 1.0 V and V<sub>gs</sub> = 1.0 V, and V<sub>gs</sub> = 5.0 V.

In conclusion, we fabricated a ternary device by combining two  $SnO_2$  nanowire channels with different  $V_{th}$

values. Controlling the Vth of the nanowires is of primary importance in the fabrication of nanowire-based ternary devices. To control the amount of V<sub>th</sub> shift, a Nd:YAG laser annealing process at two wavelengths (266 and 532 nm) was implemented. Microscale laser annealing could focus and tune only the individual nanowire channels. We expect that the direct illumination of nanowires could prevent damage to the nanowires during the laser annealing process. On the basis of the result of laser annealing at two different wavelengths, the laser illumination at the 266-nm wavelength produced more positive shifts of V<sub>th</sub> than that at the 532-nm wavelength. The positive V<sub>th</sub> shift originated from the reduced number of oxygen vacancies on the surface of the oxide nanowire. As a result, we controlled V<sub>th</sub> through the microscale laser annealing process while maintaining the SS,  $I_{on}/I_{off}$ ,  $I_{on}$ , and  $\mu_{eff}$  characteristics. Therefore, the suggested trimming method in this study is expected to provide a powerful and effective means of manufacturing a variety of nanowire-based integrated circuits.

This research was supported by the Converging Research Center Program (No. 2013K000179), the Basic Science Research Program (No. 2011-0023219), and the National Research Foundation Korea (Nos. 2012R1A2A2A01013734 and 2013M3C1A3059590) through the Ministry of Science, ICT and Future Planning, Korea.

- <sup>1</sup>W. Gang, C. Li, and L. Qin, J. Semicond. **30**, 025011 (2009).

- <sup>2</sup>X. W. Wu and F. P. Prosser, IEE Proc. G 137, 21–27 (1990).

- <sup>3</sup>F. Toto and R. Saletti, Electron. Lett. **34**, 1083 (1998).

- <sup>4</sup>A. Heung and H. T. Mouftah, IEEE J. Solid-State Circuits **20**, 609 (1985). <sup>5</sup>C. P. T. Nguyen, T. T. Trinh, V. A. Dao, J. Raja, K. Jang, T. A. H. Le,

- S. M. Iftiquar, and J. Yi, Semicond. Sci. Technol. 28, 105014 (2013).

- <sup>6</sup>H.-W. Zan, W.-T. Chen, C.-W. Chou, C.-C. Tsai, C.-N. Huang, and H.-W. Hsueh, Electrochem. Solid-State Lett. **13**, H144 (2010).

- <sup>7</sup>S. Ju, K. Lee, M.-H. Yoon, A. Faccetti, T. J. Marks, and D. B. Janes, Nanotechnology 18, 155201 (2007).

- <sup>8</sup>K. Seo, S. Kim, D. B. Janes, M. W. Jung, K.-S. An, and S. Ju, Nanotechnology **23**, 435201 (2012).

- <sup>9</sup>J. Maeng, S. Heo, G. Jo, M. Choe, S. Kim, H. Hwang, and T. Lee, Nanotechnology **20**, 095203 (2009).

- <sup>10</sup>S. Kim, S. Kim, P. Srisungsitthisunti, C. Lee, M. Xu, P. D. Ye, M. Qi, X. Xu, C. Zhou, S. Ju, and D. B. Janes, J. Phys. Chem. C **115**, 17147 (2011).

- <sup>11</sup>S. Kim, T. Lim, and S. Ju, Nanotechnology **22**, 305704 (2011).

- <sup>12</sup>S. Pisana, C. Zhang, C. Ducati, S. Hofmann, and J. Robertson, IEEE Trans. Nanotechnol. 7, 458 (2008).

- <sup>13</sup>S. Kim, H. Kim, D. B. Janes, and S. Ju, Nanotechnology **24**, 305201 (2013).

- <sup>14</sup>T. Lim, S. Lee, M. Meyyappan, and S. Ju, Semicond. Sci. Technol. **27**, 035018 (2012).

- <sup>15</sup>S. Kim and S. Ju, J. Korean Phys. Soc. **61**, 1287 (2012).

- <sup>16</sup>C. Lee, P. Srisungsitthisunti, S. Park, S. Kim, X. Xu, K. Roy, D. B. Janes, C. Zhou, S. Ju, and M. Qi, ACS Nano 5, 1095 (2011).