## Enhancement-mode operation of multilayer MoS2 transistors with a fluoropolymer gate dielectric layer

Geonwook Yoo, Sol Lea Choi, Suelbe Lee, Byungwook Yoo, Sunkook Kim, and Min Suk Oh

Citation: Applied Physics Letters **108**, 263106 (2016); doi: 10.1063/1.4955024 View online: http://dx.doi.org/10.1063/1.4955024 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/108/26?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in

Thermally activated trap charges responsible for hysteresis in multilayer MoS2 field-effect transistors Appl. Phys. Lett. **108**, 083102 (2016); 10.1063/1.4942406

Electrical characteristics of multilayer MoS2 transistors at real operating temperatures with different ambient conditions Appl. Phys. Lett. **105**, 152105 (2014); 10.1063/1.4898584

Scaling behavior of hysteresis in multilayer MoS2 field effect transistors Appl. Phys. Lett. **105**, 093107 (2014); 10.1063/1.4894865

Intrinsic carrier mobility of multi-layered MoS2 field-effect transistors on SiO2 Appl. Phys. Lett. **102**, 123105 (2013); 10.1063/1.4799172

Comparative study of chemically synthesized and exfoliated multilayer MoS2 field-effect transistors Appl. Phys. Lett. **102**, 043116 (2013); 10.1063/1.4789975

## Enhancement-mode operation of multilayer MoS<sub>2</sub> transistors with a fluoropolymer gate dielectric layer

Geonwook Yoo,  $^1$  Sol Lea Choi,  $^1$  Suelbe Lee,  $^1$  Byungwook Yoo,  $^1$  Sunkook Kim,  $^2$  and Min Suk Oh  $^{1,a)}$

<sup>1</sup>Display Materials and Components Research Center, Korea Electronics Technology Institute, Gyeonggi 463-816, South Korea

<sup>2</sup>Multi-Functional Bio/Nano Laboratory, Kyung Hee University, Gyeonggi 446-701, South Korea

(Received 25 May 2016; accepted 17 June 2016; published online 28 June 2016)

Enhancement-mode multilayer molybdenum disulfide (MoS<sub>2</sub>) field-effect transistors (FETs), which are an immensely important component toward low-power electronics based on a two-dimensional layered semiconductor, are demonstrated using the fluoropolymer CYTOP as a gate dielectric. The fabricated devices exhibit threshold voltage ( $V_{TH}$ ) of ~5.7 V with field-effect mobility ( $\mu_{FE}$ ) of up to 82.3 cm<sup>2</sup>/V s, and the characteristics are compared with the depletion-mode characteristics of MoS<sub>2</sub> FETs with the cross-linked Poly(4-vinylphenol) gate dielectric ( $V_{TH} \sim -7.8$  V). UV photoelectron spectroscopy analysis indicates that increased surface potential due to the surface dipole effect of the fluorine group influences the positive  $V_{TH}$  shift. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4955024]

Molybdenum disulfide (MoS<sub>2</sub>), a two-dimensional transition metal dichalcogenide, has drawn great interest as a promising transistor channel material for emerging electronic devices.<sup>1–7</sup> MoS<sub>2</sub> has a direct or indirect band gap (1.2-1.8 eV)depending on a number of layers,<sup>8</sup> a high mobility ( $\sim 200 \text{ cm}^2$ / V·s) with a high-k dielectric layer,<sup>9</sup> and absence of dangling bonds.<sup>10</sup> These unique properties have been facilitating intensive research efforts to address fundamental electrical and optical properties<sup>10–12</sup> and to investigate electrical contacts<sup>13–15</sup> and interface layers.<sup>16,17</sup> Furthermore, various basic and integrated electronic components for broad applications have been demonstrated based on mono- and multi-layered MoS2 fieldeffect transistors (FETs).<sup>4–7</sup> Despite all the benefits, MoS<sub>2</sub> shows a very undesirable feature for highly integrated lowpower circuits and systems; in many of the reported works,<sup>10,12,14–17</sup> MoS<sub>2</sub> FETs operate in a depletion-mode (i.e., a negative threshold voltage,  $V_{\rm TH}$ ). In other words, large negative gate-bias, not zero bias, must be applied in order to turn off the MoS<sub>2</sub> FETs since significant mobile carriers are already present in the channel even at a zero gate-bias condition. This feature requires a constant negative gate-bias to keep them offstate, resulting in a significant amount of power consumption as well as gate-bias stress effect. Therefore, an enhancementmode operation (i.e., a positive  $V_{TH}$ ) of MoS<sub>2</sub> FETs is of paramount importance to power-efficient circuits and low-power flexible electronics based on MoS<sub>2</sub>.<sup>18</sup>

Although it has been recently reported that  $V_{\rm TH}$  of MoS<sub>2</sub> FETs can be controlled by engineering the gate-metal work function,<sup>4</sup> treating sulfur vacancies,<sup>19</sup> and other approaches,<sup>20–22</sup> the tunable range of  $V_{TH}$  is rather small (<1 V) or the scheme itself is a highly elaborated method. An alternative approach can be a modulation of interface energy level by introducing additional self-assembled monolayers (SAMs), which contain a functional group on the molecular ends, at the interface between the semiconductor and gate

dielectric.<sup>23</sup> The ultra-thin SAM layer with different functional groups would have different electron-withdrawing properties and, therefore, modulate the charge carrier density in the channel. CYTOP<sup>TM</sup>, an amorphous fluoropolymer, is known to have strong hydrophobicity and electron-withdrawing property compared to Poly(4-vinylphenol) (PVP).<sup>24,25</sup> In this study, we demonstrate enhancement-mode multilayer MoS<sub>2</sub> FETs by adopting CYTOP as a gate dielectric, and compare their electrical characteristics with the same device structure except the Poly (4-vinylphenol) [PVP] dielectric. The electrical properties of the polymer thin-films as a gate dielectric are characterized by performing UV photoelectron spectroscopy (UPS) analysis and C-V measurement on a metal-insulator-metal (MIM) structure. Moreover, statistical variations of  $V_{\rm TH}$ , subthreshold swing (SS) and field-effect mobility ( $\mu_{FE}$ ) are also compared and discussed, confirming the dielectric effects.

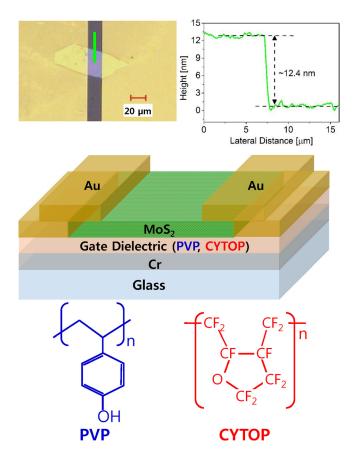

Figure 1 illustrated the fabricated multilayered MoS<sub>2</sub> FETs with the CYTOP and cross-linked PVP gate dielectrics. The chrome (Cr) glass with a Cr thickness of 90 nm was used as a back-gate electrode. Two polymer gate dielectrics were formed onto the Cr/glass as follows: (i) Poly-vinyl phenol (PVP) and poly(melamine-co-formaldehyde) [PMF], which is a cross-linking agent (1:1 mole ratio), were dissolved in propylene glycol methyl ether acetate [PGMEA] solvent ( $\sim 10\%$  wt.). Then the PVP gate dielectric layer was formed by spin-coating the solution at 3000 rpm for 60 s, followed by cross-linking for 30 min at 150 °C. (ii) CYTOP (3M, CTX-SP2) gate dielectric was formed simply by spin-coating a commercial product (3M, SP2) at 1500 rpm for 60 s, followed by curing at 70 °C for 30 min and baking at 180 °C for 60 min. The chemical structures of PVP and CYTOP are presented on the right-hand side of Fig. 1. Following the gate dielectric formation, mechanically exfoliated MoS<sub>2</sub> flakes from bulk MoS<sub>2</sub> crystals (Graphene market, USA) by a conventional scotch-tape method were transferred onto the polymer gate dielectrics. The atomic force microscopy (AFM) profile of the MoS<sub>2</sub>

<sup>&</sup>lt;sup>a)</sup>Electronic mail: ohms@keti.re.kr

FIG. 1. 3D cross-sectional schematic view of  $MoS_2$  FET with the polymer gate dielectric and its optical image with the AFM thickness profile (left). Chemical structures of the PVP (blue) and CYTOP (red) thinfilms (right).

channel in Fig. 1 confirms the thickness of ~12.4 nm. Au (80 nm) as source/drain (S/D) electrodes was deposited by thermal evaporation and then patterned using conventional photolithography followed by wet chemical etching (Transene, GE-8148). The thickness of the MoS<sub>2</sub> channel and other device dimensions (W/L) were identified using AFM and an optical microscope, respectively. Currentvoltage (*I-V*) and capacitance-voltage (*C-V*) measurements were performed using a semiconductor parameter analyzer (HP 4156A) and Precision LCR meter (Agilent 4284A), respectively.

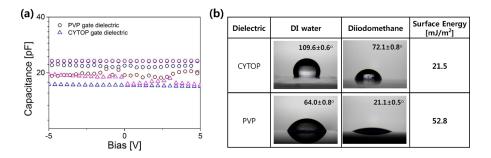

The characteristics of the prepared polymer layers as a gate dielectric are summarized in Table I. The thicknesses of the PVP and CYTOP dielectric layers were  $\sim$ 400 nm and  $\sim$ 280 nm, respectively, which were measured using the surface profiler (Tencor, P10). Both PVP and CYTOP layers exhibited quite smooth surface with rms roughness (Rq) of 5.0 and 6.8 Å measured by AFM, respectively. Capacitances (*C*) of 7.95 and

TABLE I. Properties of the PVP and CYTOP films as a gate dielectric.

| Gate<br>dielectric | Film<br>thickness | Capacitance<br>(nF/cm <sup>2</sup> ) | $\mathcal{E}_{\mathbf{r}}$ | Surface<br>roughness<br>(R <sub>q</sub> , Å) | Surface<br>energy<br>(mJ/m <sup>2</sup> ) |

|--------------------|-------------------|--------------------------------------|----------------------------|----------------------------------------------|-------------------------------------------|

| СҮТОР              | $\sim 280$        | 6.59                                 | 2.04                       | 6.8                                          | 21.5                                      |

| PVP                | $\sim 400$        | 7.95                                 | 3.59                       | 5.0                                          | 52.8                                      |

6.59 nF/cm<sup>2</sup> were obtained from *C-V* measurements for the MIM (Cr/polymer layer/Al stack) structure with a capacitor area of  $2.76 \times 10^{-3}$  cm<sup>2</sup> at 1 MHz as shown in Fig. 2(a), and the dielectric constants ( $\varepsilon_r$ ) of 3.59 and 2.04 for PVP and CYTOP, respectively, were calculated from  $\varepsilon_r = (C t)/(A \varepsilon_0)$ , where *C* is the measured capacitance, *A* is the capacitor's area, *t* is the polymer dielectric thickness, and  $\varepsilon_0$  is the vacuum permittivity. Finally, the surface energies of CYTOP and PVP were determined from contact angle measurements by Owens-Wendt Method using DI water and diiodomethane as probe liquids as summarized in Fig. 2(b).

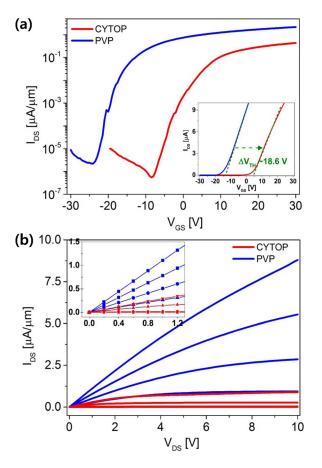

Figure 3(a) shows representative transfer curves of  $I_{\rm DS}-V_{\rm GS}$  for  $V_{\rm DS}=1$  V, in which the effect of the CYTOP gate dielectric compared with PVP on the  $V_{\rm TH}$  is clearly shown. The field-effect mobility  $(\mu_{FE})$  in a linear operation regime was extracted from  $\mu_{\rm FE} = L g_{\rm m} / (W \cdot C_{\rm OX} \cdot V_{\rm DS})$ , where W is a channel width, L is a channel length,  $C_{OX}$  is a capacitance of polymer dielectrics, and  $V_{\text{DS}}$  is drain bias of 1 V. Threshold voltage  $(V_{TH})$  was calculated using a linear extrapolation method in a linear regime  $(V_{\text{DS}} = 1 \text{ V})$ ; it was found from the intercept of a tangent at the maximum g<sub>m</sub> with  $V_{GS}$  axis. The MoS<sub>2</sub> FETs with the PVP dielectric show depletion-mode operation with significant negative  $V_{\rm TH}$  of -14 V. On the contrary, the MoS<sub>2</sub> FETs with CYTOP exhibit an enhancement-mode with  $V_{\rm TH}$  of 4.6 V, which means that the devices can be turned off at a zero gate bias. As a result, static power dissipation due to a leakage current and  $V_{\rm TH}$  instability induced by negative gate-bias stress during the off-state can be minimized. Figure 3(b) represents output characteristics  $(I_{DS}-V_{DS})$  for  $V_{GS}=0$ , 5, 10, 15 V, exhibiting an ohmic-like linear behavior at low  $V_{DS}$  and saturation at high  $V_{\text{DS}}$  bias conditions.

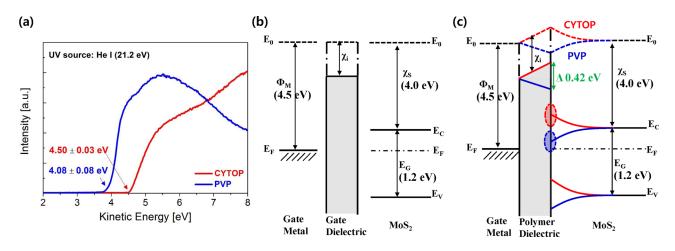

The  $V_{\text{TH}}$  shift is attributed to the strong electronwithdrawing group (i.e., fluorine) in the chemical structure of CYTOP.<sup>24,25</sup> The molecular dipole field introduced by the fluorines in the end group can induce negative charges at the MoS<sub>2</sub>-CYTOP interface, resulting in the shift of surface potential toward higher energy. UV photoelectron spectrometer measurement (AXIS Ultra DLD; Source: He I, 21.2 eV) was employed to convince and estimate a relative surface potential shift. To avoid charging effect, thin layer of both

FIG. 2. (a) C-V measurements for MIM (Cr/polymer layer/Al stack) structure with a capacitor area of  $2.76 \times 10^{-3}$  cm<sup>2</sup> at 1 MHz using the LCR meter (Agilent 4284A). (b) Contact angle measurement of both gate dielectric surfaces, and calculated surface energies using the "Owens-Wendt Method."

Reuse of AIP Publishing content is subject to the terms at: https://publishing.aip.org/authors/rights-and-permissions. Download to IP: 203.253.131.85 On: Thu, 30 Jun 2016

FIG. 3. (a) Transfer characteristics of the fabricated MoS<sub>2</sub> FETs with CYTOP (red) and PVP (blue) gate dielectrics for  $V_{\rm DS} = 1$  V.  $I_{\rm DS}$  is normalized by the devices' channel width (*W*). (Inset) The transfer characteristics in a linear scale, in which positive  $V_{\rm TH}$  shift is clearly shown. (b) Output characteristics ( $I_{\rm DS}$ - $V_{\rm DS}$ ) for  $V_{\rm GS} = 0$ , 5, 10, 15 V, exhibiting good linearity at low  $V_{\rm DS}$  (as shown in the inset) and saturation at high  $V_{\rm DS}$  conditions.

polymer dielectrics (~13 nm) was prepared. Figure 4(a) shows that the onset point of secondary electrons from the CYTOP ( $4.50 \pm 0.03 \text{ eV}$ ) was higher than the PVP ( $4.08 \pm 0.08 \text{ eV}$ ). Therefore, the work function of the CYTOP is relatively higher than that of the PVP by 0.42 eV; mobile carriers in the channel were reduced or even depleted at zero gate-bias as explained using energy band diagram in

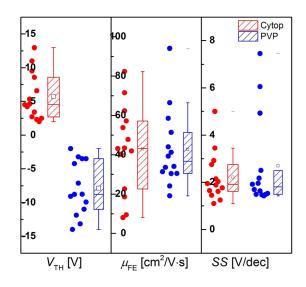

FIG. 5. Statistics of the electrical characteristics obtained from 14 devices. Threshold voltages ( $V_{\rm TH}$ ) of the measured MoS<sub>2</sub> FETs with CYTOP (red) and with of PVP (blue) dielectrics are distributed within 5.7 ± 3.5 V (enhancement mode) and  $-7.8 \pm 4.0$  V (depletion mode), respectively. However, there was no significant difference for field-effect mobility ( $\mu_{FE}$ ) and sub-threshold swing (SS).

Figs. 4(b) and 4(c). However, in the PVP or a typical oxide gate insulator, hydroxyl groups (-OH) and absorbed water molecules can induce surface charges at the gate dielectric, tuning the channel into accumulation regime.<sup>26,27</sup>

Furthermore, considering the performance variance induced by the MoS<sub>2</sub> thickness as well as fabrication process, multiple MoS<sub>2</sub> FETs were characterized in order to statistically compare electrical properties. Figure 5 shows the distribution of  $\mu_{\text{FE}}$ ,  $V_{\text{TH}}$ , and SS, which are also summarized in Table II. Above all, a depletion-mode with  $V_{\text{TH}}$  of  $-7.8 \pm 4.0$  V was exhibited for the PVP gate dielectric, and an enhancement-mode with  $V_{\text{TH}}$  of  $5.7 \pm 3.5$  V for CYTOP. There was no significant difference of  $\mu_{\text{FE}}$ , which might be attributed to the fact that even if PVP ( $\varepsilon_{\rm r} \sim 3.59$ ) has a higher dielectric constant than CYTOP's ( $\varepsilon_{\rm r} \sim 2.04$ ), other factors such as MoS<sub>2</sub> thickness, defects and other surface conditions affect  $\mu_{\text{FE}}$  as well.<sup>13,28</sup> Distribution of SS, which were calculated from  $SS = [d(\log_{10}I_{\rm DS})/dV_{\rm GS}]^{-1}$ , indicates that the

FIG. 4. (a) UPS spectrum of the CYTOP (red) and PVP (blue) gate dielectrics; a relatively higher onset point (0.42 eV) of CYTOP was observed in comparison to PVP. Schematic energy band diagram (b) of the typical isolated gate metal, gate dielectric, and MoS<sub>2</sub>, and (c) of the fabricated MoS<sub>2</sub> FETs with the CYTOP (red) and PVP (blue) gate dielectrics with no applied gate voltage. MoS<sub>2</sub>-PVP induces mobile carriers accumulated in the channel (i.e., depletion-mode), and MoS<sub>2</sub>-CYTOP reduces and depletes mobile carriers in the channel (i.e., enhancement-mode).

TABLE II. Electrical parameters of the fabricated  $MoS_2$  FETs (14 devices) containing PVP and CYTOP gate dielectrics, respectively.

| Gate dielectric | $V_{\mathrm{TH}}\left(\mathrm{V} ight)$ | $\mu_{\rm FE}~({\rm cm}^2/{\rm V~s})$ | SS (V/dec)  |

|-----------------|-----------------------------------------|---------------------------------------|-------------|

| СҮТОР           | $5.7 \pm 3.5$                           | $43.0 \pm 22.3$                       | $2.2\pm1.0$ |

| PVP             | $-7.8 \pm 4.0$                          | $42.7\pm19.7$                         | $2.7\pm1.9$ |

interface quality of MoS<sub>2</sub>-PVP was similar to MoS<sub>2</sub>-CYTOP interface.

In this work, we have fabricated and characterized enhancement-mode multilayer MoS2 FETs using the amorphous fluoropolymer CYTOP as a gate dielectric. The fabricated devices exhibited positive  $V_{\rm TH}$  of 5.7  $\pm$  3.5 V with  $\mu_{\rm FE}$ of up to  $82.3 \text{ cm}^2/\text{V}$  s. In comparison, MoS<sub>2</sub> FETs with the cross-linked PVP dielectric showed a depletion-mode with  $V_{\rm TH}$  of  $-7.8 \pm 4.0$  V. The surface dipole effect induced by the strong electron-withdrawing fluorine groups in CYTOP increases the surface potential by 0.42 eV, resulting in reduced mobile carriers in the channel and thus the positive shift of  $V_{\text{TH}}$ . The results suggest that the operation modes of multilayer MoS<sub>2</sub> FETs can be controlled by engineering the gate dielectric material. Furthermore, a direct-coupled FET logic based on MoS<sub>2</sub>, which is a basic building block for low-power digital circuits, can be realized by integrating both enhancement- and depletion-mode MoS<sub>2</sub> FETs.

This work was supported by the Industrial Strategic Technology Development Program (Grant No. 10045145) and funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea).

<sup>1</sup>S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J.-B. Yoo, J.-Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, and K. Kim, "High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals," Nat Commun. **3**, 1011 (2012).

- <sup>2</sup>G.-H. Lee, Y.-J. Yu, X. Cui, N. Petrone, C.-H. Lee, M. S. Choi, D.-Y. Lee, C. Lee, W. J. Yoo, K. Watanabe, T. Taniguchi, C. Nuckolls, P. Kim, and J. Hone, "Flexible and transparent MoS<sub>2</sub> field-effect transistors on hexagonal boron nitride-graphene heterostructures," ACS Nano 7, 7931 (2013).

- <sup>3</sup>J. Yoon, W. Park, G.-Y. Bae, Y. Kim, H. S. Jang, Y. Hyun, S. K. Lim, Y. H. Kahng, W.-K. Hong, B. H. Lee, and H. C. Ko, "Highly flexible and transparent multilayer MoS<sub>2</sub> transistors with graphene electrodes," Small **9**, 3295 (2013).

- <sup>4</sup>H. Wang, L. Yu, Y.-H. Lee, Y. Shi, A. Hsu, M. L. Chin, L.-J. Li, M. Dubey, J. Kong, and T. Palacios, "Integrated circuits based on bilayer MoS<sub>2</sub> transistors," Nano Lett. **12**, 4674 (2012).

- <sup>5</sup>R. Cheng, S. Jiang, Y. Chen, Y. Liu, N. Weiss, H.-C. Cheng, H. Wu, Y. Huang, and X. Duan, "Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics," Nat Commun. 5, 5143 (2014).

<sup>6</sup>J. Pu, L.-J. Li, and T. Takenobu, "Flexible and stretchable thin-film transistors based on molybdenum disulphide," Phys. Chem. Chem. Phys. 16, 14996 (2014).

- <sup>7</sup>D. Akinwande, N. Petrone, and J. Hone, "Two-dimensional flexible nanoelectronics," Nat Commun. 5, 5678 (2014).

- <sup>8</sup>K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, "Atomically thin MoS: A new direct-gap semiconductor," Phys. Rev. Lett. **105**, 136805 (2010).

- <sup>9</sup>L. Liu, S. B. Kumar, Y. Ouyang, and J. Guo, "Performance limits of monolayer transition metal dichalcogenide transistors," IEEE Trans. Electron Devices 58, 3042 (2011).

- <sup>10</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," Nat. Nanotechnol. 6, 147 (2011).

- <sup>11</sup>Z. Yin, H. Li, H. Li, L. Jiang, Y. Shi, Y. Sun, G. Lu, Q. Zhang, X. Chen, and H. Zhang, "Single-layer MoS<sub>2</sub> phototransistors," ACS Nano 6, 74 (2012).

- <sup>12</sup>K. Cho, T.-Y. Kim, W. Park, J. Park, D. Kim, J. Jang, H. Jeong, S. Hong, and T. Lee, "Gate-bias stress-dependent photoconductive characteristics of multilayer MoS<sub>2</sub> field-effect transistors," Nanotechnology **25**, 155201 (2014).

- <sup>13</sup>S. Das, H.-Y. Chen, A. V. Penumatcha, and J. Appenzeller, "High performance multi-layer MoS<sub>2</sub> transistors with scandium contacts," Nano Lett. **13**, 100 (2013).

- <sup>14</sup>Y. Du, L. Yang, H. Liu, and P. D. Ye, "Contact research strategy for emerging molybdenum disulfide and other two-dimensional field-effect transistors," APL Mater. 2, 092510 (2014).

- <sup>15</sup>G. Yoo, S. Lee, B. Yoo, C. Han, S. Kim, and M. S. Oh, "Electrical contact analysis of multilayer MoS<sub>2</sub> transistor with molybdenum source/drain electrodes," IEEE Electron Device Lett. **36**, 1215 (2015).

- <sup>16</sup>H. Liu and P. D. Ye, "MoS<sub>2</sub> dual-gate MOSFET with atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> as top-gate dielectric," IEEE Electron Device Lett. **33**, 546 (2012).

- <sup>17</sup>X. Zou, J. Wang, C.-H. Chiu, Y. Wu, X. Xiao, C. Jiang, W.-W. Wu, L. Mai, T. Chen, J. Li, J. C. Ho, and L. Liao, "Interface engineering for high-performance top-gated MoS<sub>2</sub> field-effect transistors," Adv. Mater. 26, 6255 (2014).

- <sup>18</sup>C. Zhou, X. Wang, S. Raju, Z. Lin, D. Villaroman, B. Huang, H. L. Chan, M. Chan, and Y. Chai, "Low voltage and high ON/OFF ratio field-effect transistors based on CVD MoS<sub>2</sub> and ultra high-k gate dielectric PZT," Nanoscale 7, 8695 (2015).

- <sup>19</sup>W. S. Leong, Y. Li, X. Luo, C. T. Nai, S. Y. Quek, and J. T. L. Thong, "Tuning the threshold voltage of MoS<sub>2</sub> field-effect transistors via surface treatment," Nanoscale 7, 10823 (2015).

- <sup>20</sup>H. S. Lee, J. M. Shin, P. J. Jeon, J. Lee, J. S. Kim, H. C. Hwang, E. Park, W. Yoon, S.-Y. Ju, and S. Im, "Few-layer MoS<sub>2</sub>–Organic thin-film hybrid complementary inverter pixel fabricated on a glass substrate," Small 11, 2132 (2015).

- <sup>21</sup>K. Choi, Y. T. Lee, S.-W. Min, H. S. Lee, T. Nam, H. Kim, and S. Im, "Direct imprinting of MoS<sub>2</sub> flakes on a patterned gate for nanosheet transistors," J. Mater. Chem. C 1, 7803 (2013).

- <sup>22</sup>H. Liu, J. Gu, and P. Ye, "MoS<sub>2</sub> nanoribbon transistors: Transition from depletion-mode to enhancement-mode by channel width trimming," IEEE Electron Device Lett. **33**, 1273 (2012).

- <sup>23</sup>Y. Jang, J. H. Cho, D. H. Kim, Y. D. Park, M. Hwang, and K. Cho, "Effects of the permanent dipoles of self-assembled monolayer-treated insulator surfaces on the field-effect mobility of a pentacene thin-film transistor," Appl. Phys. Lett. **90**, 132104 (2007).

- <sup>24</sup>M. Park, J. Jang, S. Park, J. Kim, J. Seong, J. Hwang, and C. E. Park, "The effects of organic material-treated SiO<sub>2</sub> dielectric surfaces on the electrical characteristics of inorganic amorphous In-Ga-Zn-O thin film transistors," Appl. Phys. Lett. **100**, 102110 (2012).

- <sup>25</sup>S. H. Kim, S. Nam, J. Jang, K. Hong, C. Yang, D. S. Chung, C. E. Park, and W.-S. Choi, "Effect of the hydrophobicity and thickness of polymer gate dielectrics on the hysteresis behavior of pentacene-based field-effect transistors," J. Appl. Phys. **105**, 104509 (2009).

- <sup>26</sup>M. P. Walser, W. L. Kalb, T. Mathis, T. J. Brenner, and B. Batlogg, "Stable complementary inverters with organic field-effect transistors on CYTOP fluoropolymer gate dielectric," Appl. Phys. Lett. **94**, 053303 (2009).

- <sup>27</sup>Y. Guo, X. Wei, J. Shu, B. Liu, J. Yin, C. Guan, Y. Han, S. Gao, and Q. Chen, "Charge trapping at the MoS<sub>2</sub>-SiO<sub>2</sub> interface and its effects on the characteristics of MoS<sub>2</sub> metal-oxide-semiconductor field effect transistors," Appl. Phys. Lett. **106**, 103109 (2015).

- <sup>28</sup>J. Kang, W. Liu, and K. Banerjee, "High-performance MoS<sub>2</sub> transistors with low-resistance molybdenum contacts," Appl. Phys. Lett. **104**, 093106 (2014).